電子ブロック工房:

Deprecated: Function strftime() is deprecated in /home/u109394186/domains/rad51.net/public_html/jeans/jeans/libs/blog.php on line 333

2007年 07月の記事

6 bit CPU [CPU]

2007年7月27日

ばかげた 1 bit CPU を考えていて気が付いたのは、6ビットCPUが結構シンプルに設計できそうなこと。先日のクロック周りの回路の設計から来る考察をくわえて、さらにシンプルなCPUが出来そうな気配。

今考えているのは、6ビットのレジスタとして、

a: アキュムレータ

b: メモリ指定用レジスタ

ds: データセグメント

ip: インデックスポインタ(プログラムカウンタ)

cs: コードセグメント

sp: スタックポインタ

の6つを用意。アドレス空間は、12ビットのアドレスラインで4096ワード(3072ビット)。簡単なプログラムなら、これくらいの要領があればおそらく十分。このあたり、4ビットではなくて6ビットにしたのが味噌で、2ワードのアドレスラインで必要最小限と思われるメモリ領域にアクセスできる。4ビットなら、3ワード必要だろう。74174という6ビットのフリップフロップがあるのも、良い。1つのセグメントが64ワードだから、そこそこの大きさのプログラムがここに収まる。4ビットの考え方だと16ワードで、小さなプログラムしかかけない。ジャンプ命令の仕様で難が出る。

スタックセグメントは、6502に習って省略した。従って、スタック領域は64ワードのみ。フラグは、例によってキャリーとゼロの2つだけである。

今考えているのは、6ビットのレジスタとして、

a: アキュムレータ

b: メモリ指定用レジスタ

ds: データセグメント

ip: インデックスポインタ(プログラムカウンタ)

cs: コードセグメント

sp: スタックポインタ

の6つを用意。アドレス空間は、12ビットのアドレスラインで4096ワード(3072ビット)。簡単なプログラムなら、これくらいの要領があればおそらく十分。このあたり、4ビットではなくて6ビットにしたのが味噌で、2ワードのアドレスラインで必要最小限と思われるメモリ領域にアクセスできる。4ビットなら、3ワード必要だろう。74174という6ビットのフリップフロップがあるのも、良い。1つのセグメントが64ワードだから、そこそこの大きさのプログラムがここに収まる。4ビットの考え方だと16ワードで、小さなプログラムしかかけない。ジャンプ命令の仕様で難が出る。

スタックセグメントは、6502に習って省略した。従って、スタック領域は64ワードのみ。フラグは、例によってキャリーとゼロの2つだけである。

クロック周り3 [デジタル回路]

2007年7月23日

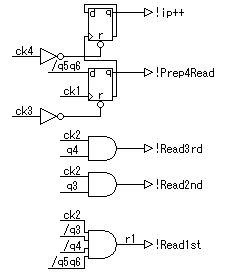

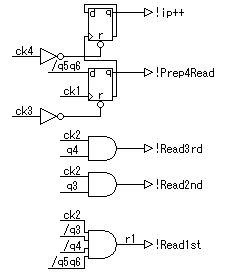

ip++信号を、Prep4Read 信号近くに作成した。

ここで、問題が発覚。ipレジスタのやり取りをするジャンプ系命令の実行の際、上記のip++信号が下がるときと、命令実行信号の立ち上がり(ipレジスタへの代入をトリガー)が同じタイミングで起こる。ICの性質によっては、2回のトリガーが重なって、1回だけのトリガーになってしまう可能性がある。ip++ のあと、一呼吸してから ip 代入命令を実行すればよいのであるが、もともとジャンプ系の命令はすべてダブルクロックで実行されるので、この辺りの設計を変えなければならない。

そこで、ダブルクロック命令の実行の際は、1回休んでから命令の実行を開始することにした。したがって、ダブルクロック命令の実行には、3クロック消費されることになる。

ここで、問題が発覚。ipレジスタのやり取りをするジャンプ系命令の実行の際、上記のip++信号が下がるときと、命令実行信号の立ち上がり(ipレジスタへの代入をトリガー)が同じタイミングで起こる。ICの性質によっては、2回のトリガーが重なって、1回だけのトリガーになってしまう可能性がある。ip++ のあと、一呼吸してから ip 代入命令を実行すればよいのであるが、もともとジャンプ系の命令はすべてダブルクロックで実行されるので、この辺りの設計を変えなければならない。

そこで、ダブルクロック命令の実行の際は、1回休んでから命令の実行を開始することにした。したがって、ダブルクロック命令の実行には、3クロック消費されることになる。

クロック周り2 [デジタル回路]

2007年7月23日

目的に合うように、先日のクロック周りの回路をさらに拡張していくうちに、スパゲッティの様な回路になってしまった。もしかしたらうまく働くのかもしれないが、おそらく誤作動するだろう。

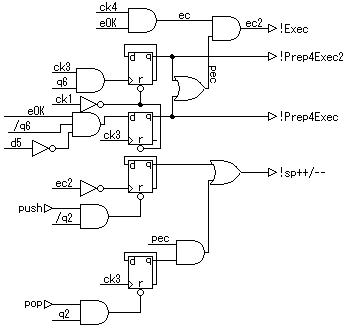

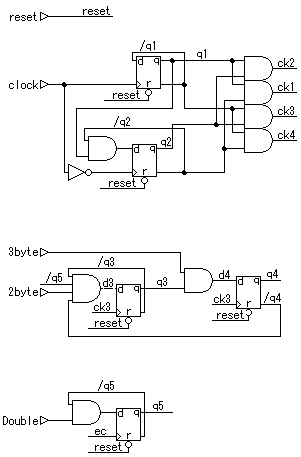

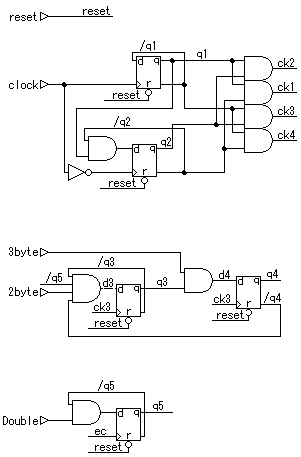

源内CADの使い方にも慣れてきたので、一から作り直すことにした。今回の回路は、systematic に仕上がっているので、拡張性が高くバグの混入の可能性も低いと思われる。新しいタイミング回路のメイン部分は次のとおり。

上の回路は、水晶発信からのシグナルを4つのクロックに分解する部分。2つ目のFFのデータ入力部に、AND回路を入れた。これを入れなかった前の回路は、リセットスイッチを押したときの水晶発信からのクロックが1か0かによって、誤作動する可能性があった。

真ん中と下の回路は、それぞれ、2バイト・3バイト命令の制御と、1つの命令で2回のクロックが必要な場合の制御。シンプルな回路に収まった(ラインecは、命令実行トリガー;記事の続きを参照)。

源内CADの使い方にも慣れてきたので、一から作り直すことにした。今回の回路は、systematic に仕上がっているので、拡張性が高くバグの混入の可能性も低いと思われる。新しいタイミング回路のメイン部分は次のとおり。

上の回路は、水晶発信からのシグナルを4つのクロックに分解する部分。2つ目のFFのデータ入力部に、AND回路を入れた。これを入れなかった前の回路は、リセットスイッチを押したときの水晶発信からのクロックが1か0かによって、誤作動する可能性があった。

真ん中と下の回路は、それぞれ、2バイト・3バイト命令の制御と、1つの命令で2回のクロックが必要な場合の制御。シンプルな回路に収まった(ラインecは、命令実行トリガー;記事の続きを参照)。

クロック周り [デジタル回路]

2007年7月19日

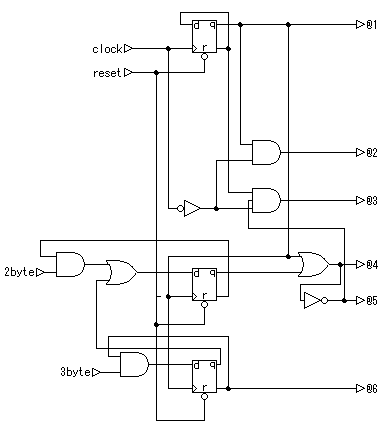

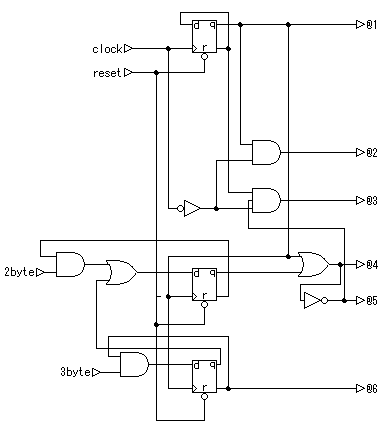

クロック周りの回路は、こんな感じで。

タイミングが難しいので、源内CADを用いて回路図を作成し、シミュレーションを行いながら回路図を完成させた。なお、この回路図の完成により、2バイト命令・3バイト命令を実現できることが分かったので、CPUの機能はこれに従って変更していくことになる。

タイミングが難しいので、源内CADを用いて回路図を作成し、シミュレーションを行いながら回路図を完成させた。なお、この回路図の完成により、2バイト命令・3バイト命令を実現できることが分かったので、CPUの機能はこれに従って変更していくことになる。

1 bit CPU [CPU]

2007年7月18日

1 bit のアキュムレータでも、CPU として機能する設計が出来そうだ。これを採用するかどうかは分からないけれど、とりあえずメモ。

レジスタは、1ビットのアキュムレータが、a0 と a1 の2つ。フラグは例によって、キャリーとゼロの2つ。メモリ読み書き用の b レジスタが6ビットである。メモリ空間は、1ワードが6ビットで、アドレスラインが12ビット。4096ワードで、これは24kビットの3kバイトに相当する。

6ビットのbレジスタは機能として、インクリメント・デクリメント・右ローテート及びメモリへの読み書きだけなので、アキュムレータとは言いがたい。

1ビットの a0, a1レジスタには、加算・減算・ビット演算機能を持たせた。演算は、a0, a1 レジスタ経由で、1ビットずつ行う。

インデックスポインタ(ip)、データポインタ(dp)、スタックポインタ(sp)は6ビットである。インデックスポインタとデータポインタはそれぞれ、コードセグメント(cs)、データセグメント(ds)と共に用いる。スタックのセグメントは固定の仕様。64ワードのスタック領域が使えるので、十分だろう。dpとspは、インクリメント・デクリメントの両方が、ip はインクリメントが出来る。

ip と cs には、もう一つのペア(ip', cs')があり、ジャンプ命令やユーザー定義命令の際に、ip と cs のコピーがこれらのレジスタに渡される。インクリメントが可能で、メモリ内容をbレジスタに渡すことが可能。

なお、ゼロフラグは、インクリメント・デクリメントのときのみ影響を受ける仕様。

ニーモニックの052-056と060-077の部分はユーザ定義命令で、ジャンプ命令などもここに含まれている。アドレスの00020-00277の部分に、これら用のプログラムを書き込む。00300-00377の部分も、ユーザ定義命令のサブルーチンとして使用予定なので、実際にプログラムが書き込めるのは00400-00677 の部分だけである(容量が足りないか?)。00700-00777にはRAMを持たせて、データの保持及びスタック領域に用いる。

1 bit registers and flags: a0, a1, z, c 6 bit registers: b, ip, cs, ip', cs', dp, ds, sp

レジスタは、1ビットのアキュムレータが、a0 と a1 の2つ。フラグは例によって、キャリーとゼロの2つ。メモリ読み書き用の b レジスタが6ビットである。メモリ空間は、1ワードが6ビットで、アドレスラインが12ビット。4096ワードで、これは24kビットの3kバイトに相当する。

6ビットのbレジスタは機能として、インクリメント・デクリメント・右ローテート及びメモリへの読み書きだけなので、アキュムレータとは言いがたい。

1ビットの a0, a1レジスタには、加算・減算・ビット演算機能を持たせた。演算は、a0, a1 レジスタ経由で、1ビットずつ行う。

インデックスポインタ(ip)、データポインタ(dp)、スタックポインタ(sp)は6ビットである。インデックスポインタとデータポインタはそれぞれ、コードセグメント(cs)、データセグメント(ds)と共に用いる。スタックのセグメントは固定の仕様。64ワードのスタック領域が使えるので、十分だろう。dpとspは、インクリメント・デクリメントの両方が、ip はインクリメントが出来る。

ip と cs には、もう一つのペア(ip', cs')があり、ジャンプ命令やユーザー定義命令の際に、ip と cs のコピーがこれらのレジスタに渡される。インクリメントが可能で、メモリ内容をbレジスタに渡すことが可能。

なお、ゼロフラグは、インクリメント・デクリメントのときのみ影響を受ける仕様。

ニーモニックの052-056と060-077の部分はユーザ定義命令で、ジャンプ命令などもここに含まれている。アドレスの00020-00277の部分に、これら用のプログラムを書き込む。00300-00377の部分も、ユーザ定義命令のサブルーチンとして使用予定なので、実際にプログラムが書き込めるのは00400-00677 の部分だけである(容量が足りないか?)。00700-00777にはRAMを持たせて、データの保持及びスタック領域に用いる。

4 bit CPU [CPU]

2007年7月16日

少し思うところあって、4ビットのCPUの設計を検討することにする。理由は、

1)当然ながら8ビットから4ビットに落とすことによって、回路を約半分の大きさに出来ること。

2)ローテート命令をCPUに持たせることにより、加算・減算ルーチンが容易に組めることに気が付いたこと(6502 ではシフト命令がなくて、ローテート命令だけがあることを知った)。

仕様としては4ビットだが、複合命令として8ビットの加算・減算に対応しており、それほどはプログラミングが煩雑にならない様子。ただし、当然ながら、8ビットから4ビットに変更することで、スピードは落ちるはず。

思い切って1ビットのCPUというのも考えたが、この場合はメモリへの読み書きに難が出る。1ビットCPUの設計がうまく出来れば、トランジスタコンピューターの完成も近くなりそうだけれど。

1)当然ながら8ビットから4ビットに落とすことによって、回路を約半分の大きさに出来ること。

2)ローテート命令をCPUに持たせることにより、加算・減算ルーチンが容易に組めることに気が付いたこと(6502 ではシフト命令がなくて、ローテート命令だけがあることを知った)。

仕様としては4ビットだが、複合命令として8ビットの加算・減算に対応しており、それほどはプログラミングが煩雑にならない様子。ただし、当然ながら、8ビットから4ビットに変更することで、スピードは落ちるはず。

思い切って1ビットのCPUというのも考えたが、この場合はメモリへの読み書きに難が出る。1ビットCPUの設計がうまく出来れば、トランジスタコンピューターの完成も近くなりそうだけれど。

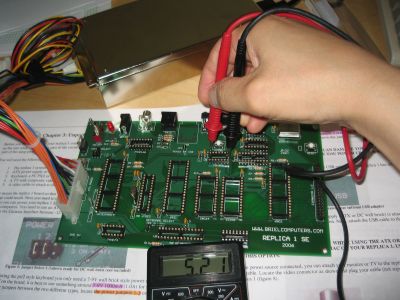

My Apple I Replica [一般的なこと]

2007年7月2日

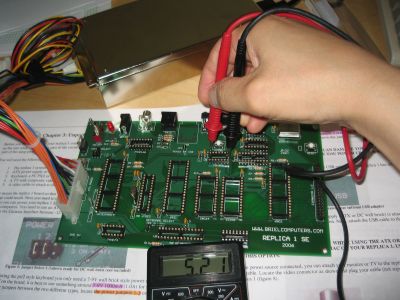

Briel Computersに注文してあった Apple I Replica I のキットが先週届いていたので、この週末に組み立てた。このキットの基盤は半田ののりが非常に良く、トラブルもほとんど無く半田付け完了。3-4時間で完成した。

まずは、キットの説明書きにあったように、電源を入れた状態でICに来ている電圧をチェック。

ちゃんと5Vが来ていることを確認した。

ちゃんと5Vが来ていることを確認した。

まずは、キットの説明書きにあったように、電源を入れた状態でICに来ている電圧をチェック。