シミュレーション

| Jeans & Development | 電子ブロック工房 | 三日坊主 | フロントページ |

Verilogを使ってみた [シミュレーション]

2011年7月2日

今の時代、デジタル回路を考える際、HDL (Hardware Description Language)を会得するのは必須のようらしい。FGPAなどの応用範囲もある。覚えておいて損はない、言語だろう。

VHDLとVerilogの両方を試してみたが、Verilogの方が自分には合っているようだ。

VHDLとVerilogの両方を試してみたが、Verilogの方が自分には合っているようだ。

回路進捗 [シミュレーション]

2009年9月18日

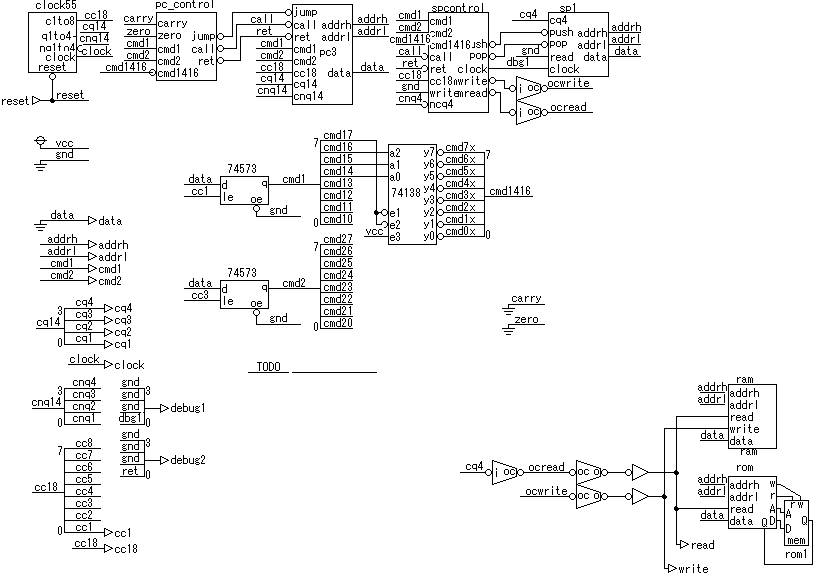

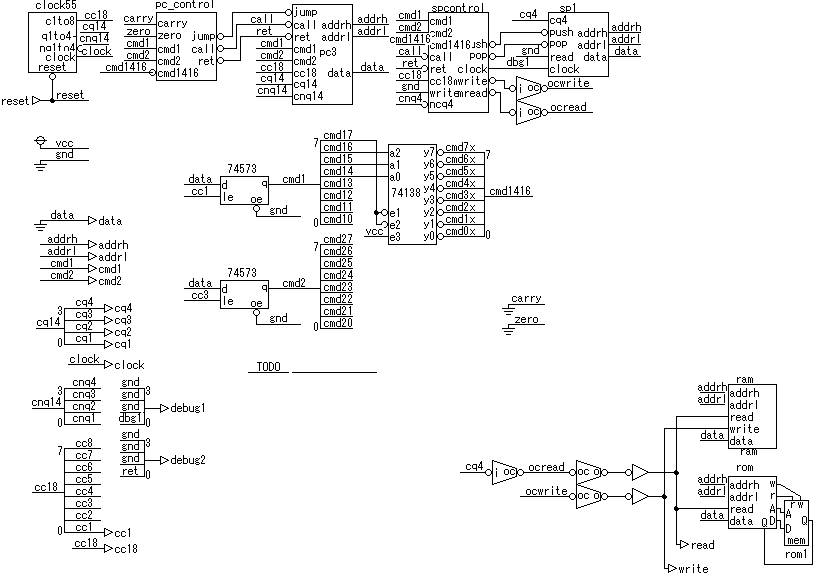

現在の回路は源内CADで書かれており、次のとおり。

(<%media(20090919-main_0063_06.zip|ここからダウンロード)%>)

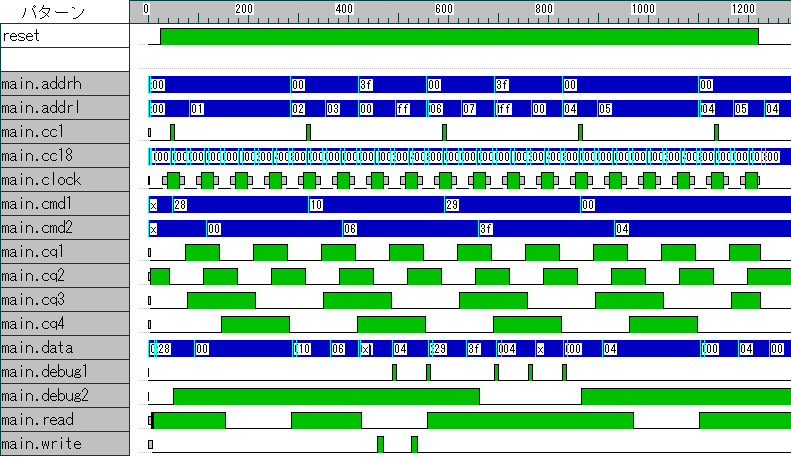

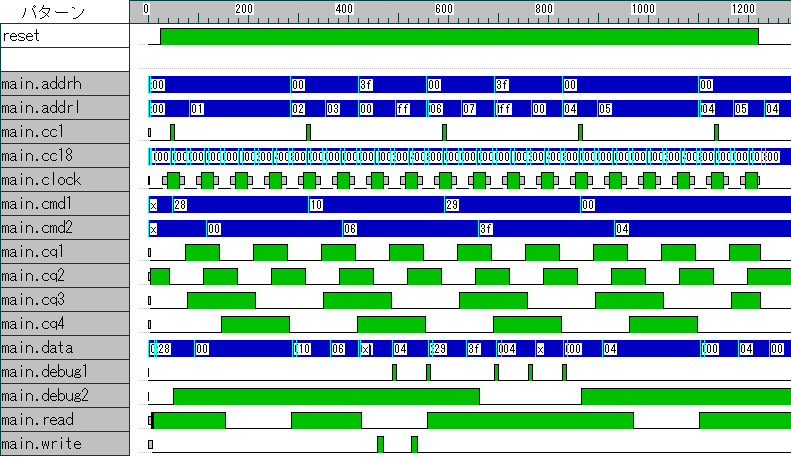

シミュレーションの結果は、次のとおり。

(<%media(20090919-main_0063_06.zip|ここからダウンロード)%>)

シミュレーションの結果は、次のとおり。

JK-FF [シミュレーション]

2009年8月9日

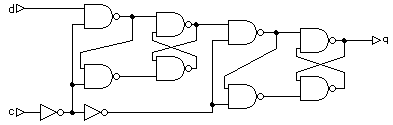

JKタイプのフリップフロップの勉強。これを今まであまりよく理解していなかった。もしかしたら便利な場面が出てくるかもしれないので…。

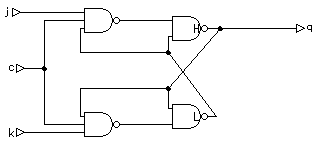

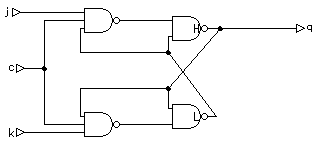

まず、Wikipediaに載っている最も簡単な回路を再現してみた。

回路図中でNANDゲートにHやLが有るのは、シミュレーション開始時にデフォルトでHやLを出力するように改変した特殊なもの。これを入れることで、無事にシミュレーションが開始する。

ところが、どうもうまくいかない。j=Hのときにクロックを与えると(この回路では、短い幅のクロックを与えないといけないらしい)ちゃんと設定される。しかし、k=Hのときだと、どんな形のクロックを与えても、必ず発振してしまう。

まず、Wikipediaに載っている最も簡単な回路を再現してみた。

回路図中でNANDゲートにHやLが有るのは、シミュレーション開始時にデフォルトでHやLを出力するように改変した特殊なもの。これを入れることで、無事にシミュレーションが開始する。

ところが、どうもうまくいかない。j=Hのときにクロックを与えると(この回路では、短い幅のクロックを与えないといけないらしい)ちゃんと設定される。しかし、k=Hのときだと、どんな形のクロックを与えても、必ず発振してしまう。

Verilogライクなシミュレータ [シミュレーション]

2009年2月24日

C++で次のように書ける、ロジック回路のシミュレータを作ってみた。

これは、NANDを二つつなげただけの、もっともシンプルなフリップフロップ。前にPHPで書いたものと違って、今回のは回路の内の遅延などもシミュレーションできるようにしてある。なので、ラッチやフリップフロップを組み合わせた複雑な回路のシミュレーションにも使えるはず。

使ったことないし良く分からないが、Verilogというものに構文が良く似ているようだ。既存のソフトの使い方を覚えるより、使いにくくても自作して細かな調整を自身で行うほうが、私には向いている。今回のシミュレータは、遅延時間を素子ごとにランダムに設定することもできるので、多分、回路を設計するさいの動作確認にも使える。

bool input1,input2; logic* na1=nandGate(); logic* na2=nandGate(); na1->connect(&input1,&na2->output); na2->connect(&na1->output,&input2);

これは、NANDを二つつなげただけの、もっともシンプルなフリップフロップ。前にPHPで書いたものと違って、今回のは回路の内の遅延などもシミュレーションできるようにしてある。なので、ラッチやフリップフロップを組み合わせた複雑な回路のシミュレーションにも使えるはず。

使ったことないし良く分からないが、Verilogというものに構文が良く似ているようだ。既存のソフトの使い方を覚えるより、使いにくくても自作して細かな調整を自身で行うほうが、私には向いている。今回のシミュレータは、遅延時間を素子ごとにランダムに設定することもできるので、多分、回路を設計するさいの動作確認にも使える。

シミュレータが完成 [シミュレーション]

2007年6月24日

シミュレータが、(おそらく)完成した。最後に残っていた、複合命令まわりのコードを仕上げた。いくつかの複合命令を実行してみたが、うまく動いている様子。

8ビットどうしの掛け算 [シミュレーション]

2007年6月23日

新しいニーモニック表を用いたマシン語で、8ビットどうしの掛け算を行なった。このルーチンを汎用サブルーチンとしてメモリに確保しておき、これを利用する形で16ビットどうしの掛け算を行わせる予定。

シミュレータのデバッグと起動 [シミュレーション]

2007年6月18日

先日シミュレータの記事を書いた段階ではまだテストランもほとんど行っていなかったため、当然ながらバグだらけのコードであった。デバッグを行い、簡単なマシン語を実行してみた。