クロック周り2

2007年7月23日

目的に合うように、先日のクロック周りの回路をさらに拡張していくうちに、スパゲッティの様な回路になってしまった。もしかしたらうまく働くのかもしれないが、おそらく誤作動するだろう。

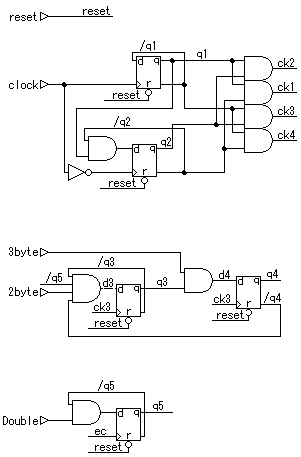

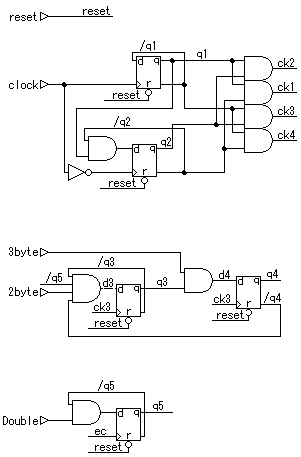

源内CADの使い方にも慣れてきたので、一から作り直すことにした。今回の回路は、systematic に仕上がっているので、拡張性が高くバグの混入の可能性も低いと思われる。新しいタイミング回路のメイン部分は次のとおり。

上の回路は、水晶発信からのシグナルを4つのクロックに分解する部分。2つ目のFFのデータ入力部に、AND回路を入れた。これを入れなかった前の回路は、リセットスイッチを押したときの水晶発信からのクロックが1か0かによって、誤作動する可能性があった。

真ん中と下の回路は、それぞれ、2バイト・3バイト命令の制御と、1つの命令で2回のクロックが必要な場合の制御。シンプルな回路に収まった(ラインecは、命令実行トリガー;記事の続きを参照)。

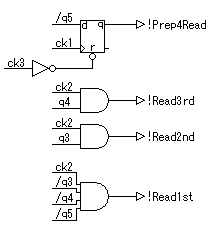

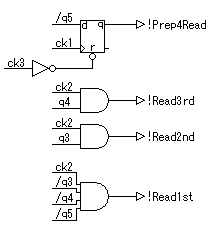

次に、命令読み取りのタイミング用回路。

Prep4Read が1のとき、[ip]の内容をメモリからデータラインに呼び出し、Read1st, Read2nd, Read3rd の立ち上がりで、データラインの内容を3つのレジスタ(74174で作成)に保存する。記事を書いていて気が付いたが、まだ ip++ 信号がない。作成しなければならない。

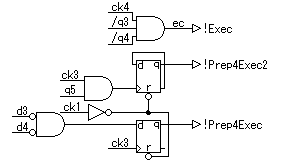

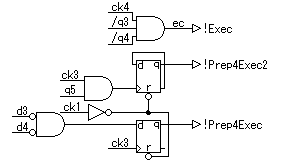

命令実行回路。

Prep4Execが1の時、データラインを実行用に準備する。さらにPrep4Exec2も1の時は、2つ目の命令の実行準備。ここで行うべき命令の内容は、上で述べた3つのレジスタに保存されている。Exec の立ち上がりで、命令を実行する。

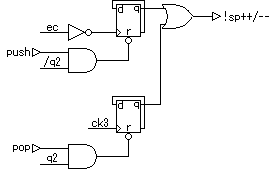

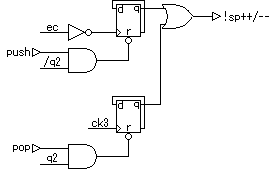

スタックポインタのinc/dec用回路。

push/pop命令の際の、sp のアップダウン用のクロックを作成する部分。

シミュレーションの結果はこのとおり。以下の命令を、順にシミューレートしてみた。

1)1バイトpush命令

2)2バイトpush命令(push の使用予定なし)

3)3バイトpush命令(push の使用予定なし)

4)1バイトpop命令

5)1バイト・2クロックpop命令(ret 命令など)

6)2バイト・2クロックpush命令(call 命令など)

7)3バイト・2クロックpush命令(call 命令など)

なお、マルチバイト・ダブルクロックのpop命令は使えない(sp++ シグナルが余分に発生する)ので注意。

源内CADの使い方にも慣れてきたので、一から作り直すことにした。今回の回路は、systematic に仕上がっているので、拡張性が高くバグの混入の可能性も低いと思われる。新しいタイミング回路のメイン部分は次のとおり。

上の回路は、水晶発信からのシグナルを4つのクロックに分解する部分。2つ目のFFのデータ入力部に、AND回路を入れた。これを入れなかった前の回路は、リセットスイッチを押したときの水晶発信からのクロックが1か0かによって、誤作動する可能性があった。

真ん中と下の回路は、それぞれ、2バイト・3バイト命令の制御と、1つの命令で2回のクロックが必要な場合の制御。シンプルな回路に収まった(ラインecは、命令実行トリガー;記事の続きを参照)。

次に、命令読み取りのタイミング用回路。

Prep4Read が1のとき、[ip]の内容をメモリからデータラインに呼び出し、Read1st, Read2nd, Read3rd の立ち上がりで、データラインの内容を3つのレジスタ(74174で作成)に保存する。記事を書いていて気が付いたが、まだ ip++ 信号がない。作成しなければならない。

命令実行回路。

Prep4Execが1の時、データラインを実行用に準備する。さらにPrep4Exec2も1の時は、2つ目の命令の実行準備。ここで行うべき命令の内容は、上で述べた3つのレジスタに保存されている。Exec の立ち上がりで、命令を実行する。

スタックポインタのinc/dec用回路。

push/pop命令の際の、sp のアップダウン用のクロックを作成する部分。

シミュレーションの結果はこのとおり。以下の命令を、順にシミューレートしてみた。

1)1バイトpush命令

2)2バイトpush命令(push の使用予定なし)

3)3バイトpush命令(push の使用予定なし)

4)1バイトpop命令

5)1バイト・2クロックpop命令(ret 命令など)

6)2バイト・2クロックpush命令(call 命令など)

7)3バイト・2クロックpush命令(call 命令など)

なお、マルチバイト・ダブルクロックのpop命令は使えない(sp++ シグナルが余分に発生する)ので注意。