タイミング回路、再び

2009年7月23日

8 bit CPU への移行に伴って、クロック周りの回路を大幅に書き換えた。

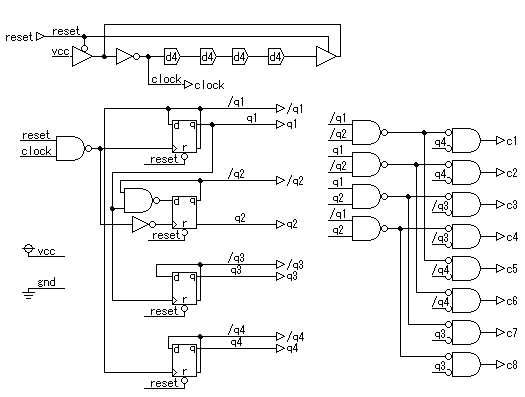

まずできたのは、<%media(20090724-clock4.zip|以下のもの)%>。

回路図上のほう、ディレイを用いた部分は発信回路で、源内CAD限定。実際には、水晶発振などで置き換える。

シミュレーションの結果は、次のとおり。

よさそうに見える。…が、一箇所気に入らない部分がある。例えば、c3は2バイト命令の2バイト目を読むために用いる信号だが、この信号がHの間、CPUが出力するアドレスラインは安定していないといけない。メモリから命令を読む際のアドレスラインは、q4がLの間、出力される。このとき、c3の下がりは、q4の上がりよりも安定して早く行われないといけないが、ここの部分が微妙なのだ。導線がちょっと長かったり、間に入れるゲートの数が微妙に違ったりすると、メモリでデータを読む際にq4の上がりがc3の下がりよりも早く行われるかもしれない。こうなると、メモリの内容を正確に読むことができなくなる。

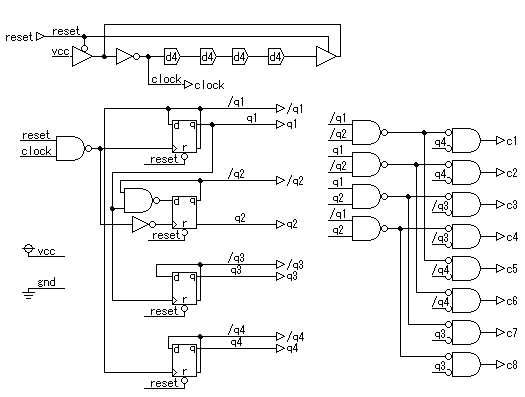

そこで改良を加えたのが、<%media(20090724-clock5.zip|次の回路)%>。

シミュレーションの結果は、以下のようになる。

ディレイ回路をうまく作るのは、後々経験や実験が必要になるだろうが、タイミング回路の設計としてはこれでよさそう。

各クロックの実際の使用例としては、例えばCALL命令の場合、

c1: 命令一バイト目読み出し

c2: PC(プログラムカウンタ)のインクリメント

c3: 命令二バイト目読み出し

c4: PCのインクリメント

c5: PCのメモリへの書き込み(上位バイト)

c6: SP(スタックポインタ)のデクリメント

c7: PCのメモリへの書き込み(下位バイト)

c8: SPのデクリメント

となる。q4がLの間、PCの内容がアドレスラインに出力され、q4がHの間、SPの内容がアドレスラインに出力される。ディレイの長さとしては、もしクロックを1 MHzとした場合に、100-200 nsが妥当だろう。これくらいの長さがあれば、手に入るSRAMの書き込み速度などと比較して問題なさそうである。実際には20ns辺りがしきいらしく、そうなるとクロックは5 MHzから10 MHzまで上げられることになる。

まずできたのは、<%media(20090724-clock4.zip|以下のもの)%>。

回路図上のほう、ディレイを用いた部分は発信回路で、源内CAD限定。実際には、水晶発振などで置き換える。

シミュレーションの結果は、次のとおり。

よさそうに見える。…が、一箇所気に入らない部分がある。例えば、c3は2バイト命令の2バイト目を読むために用いる信号だが、この信号がHの間、CPUが出力するアドレスラインは安定していないといけない。メモリから命令を読む際のアドレスラインは、q4がLの間、出力される。このとき、c3の下がりは、q4の上がりよりも安定して早く行われないといけないが、ここの部分が微妙なのだ。導線がちょっと長かったり、間に入れるゲートの数が微妙に違ったりすると、メモリでデータを読む際にq4の上がりがc3の下がりよりも早く行われるかもしれない。こうなると、メモリの内容を正確に読むことができなくなる。

そこで改良を加えたのが、<%media(20090724-clock5.zip|次の回路)%>。

シミュレーションの結果は、以下のようになる。

ディレイ回路をうまく作るのは、後々経験や実験が必要になるだろうが、タイミング回路の設計としてはこれでよさそう。

各クロックの実際の使用例としては、例えばCALL命令の場合、

c1: 命令一バイト目読み出し

c2: PC(プログラムカウンタ)のインクリメント

c3: 命令二バイト目読み出し

c4: PCのインクリメント

c5: PCのメモリへの書き込み(上位バイト)

c6: SP(スタックポインタ)のデクリメント

c7: PCのメモリへの書き込み(下位バイト)

c8: SPのデクリメント

となる。q4がLの間、PCの内容がアドレスラインに出力され、q4がHの間、SPの内容がアドレスラインに出力される。ディレイの長さとしては、もしクロックを1 MHzとした場合に、100-200 nsが妥当だろう。これくらいの長さがあれば、手に入るSRAMの書き込み速度などと比較して問題なさそうである。実際には20ns辺りがしきいらしく、そうなるとクロックは5 MHzから10 MHzまで上げられることになる。