回路進捗

2009年9月18日

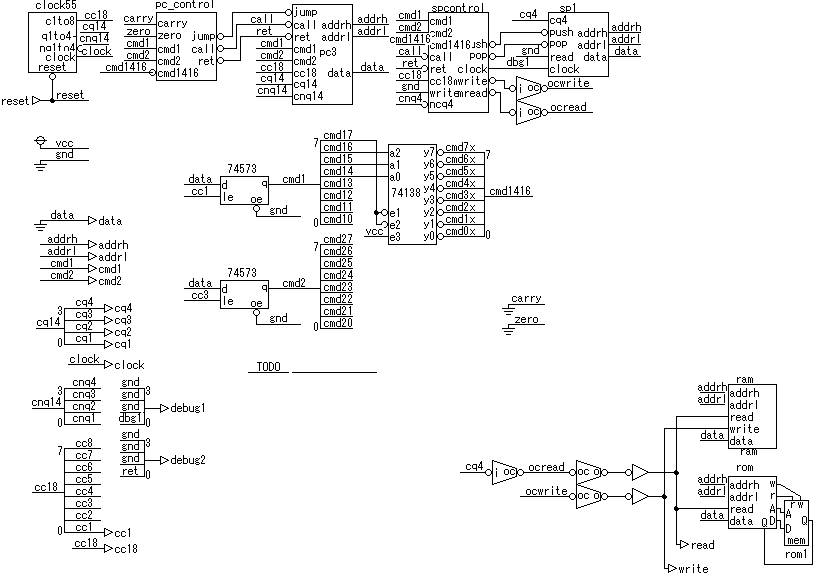

現在の回路は源内CADで書かれており、次のとおり。

(<%media(20090919-main_0063_06.zip|ここからダウンロード)%>)

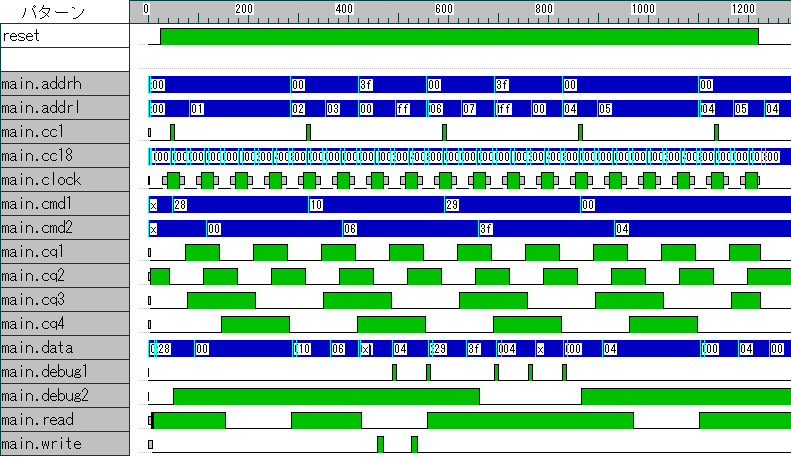

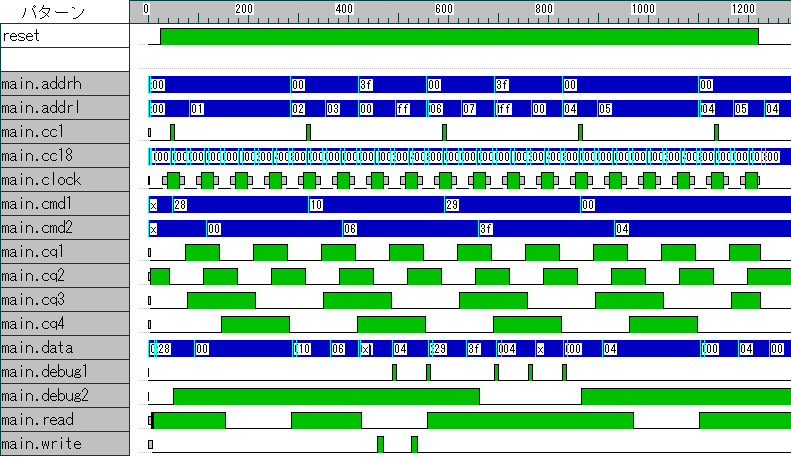

シミュレーションの結果は、次のとおり。

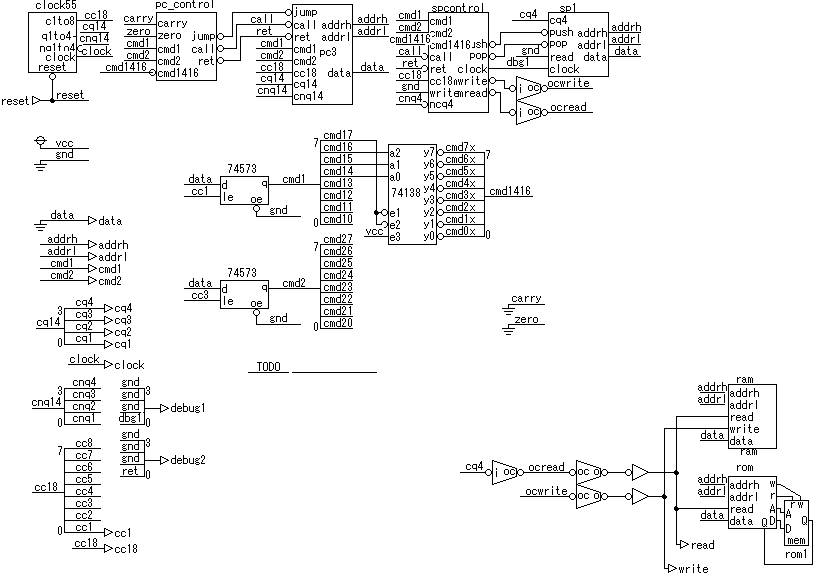

当然ながらひとつの図面では書ききれないので、いくつかのパーツに分解してある。74573と74138は、74シリーズの汎用ロジックICなので、説明は割愛。『i oc』『oc o』と書かれたパーツは、先に説明したオープンコレクタ部分の実装である。

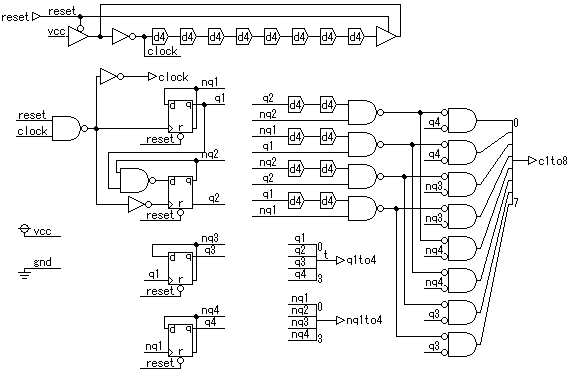

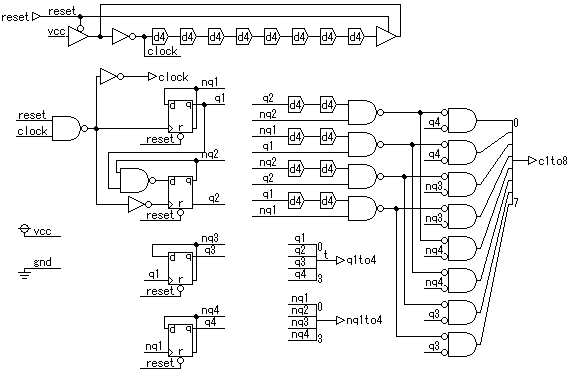

左上から順に見てゆこう。まず、clock55。これはクロックジェネレータで、回路は次のとおり。

回路の上のほう、ディレイが8つ並んでいるのは、源内CAD限定の水晶発振回路。これを作成しシミュレートすると、『xxxxで発振しました』と警告が出て停止するが、reset信号のHの長さを適当に調整すると、警告は出なくなる。その後、このreset信号のHの長さを少しずつ長くしてゆけばよい。上記回路では、非同期でフリップフロップを繋げ、8つのシグナルに分周するようにした。8つのシグナルの入力部分で、2つのディレイを用いてトリガー信号を作成している。これは、メモリやレジスタへの書き込みなどのときに使うための信号であるが、このような実装にするのかどうかは実際の回路を組むときに再考する。動作結果は、先のメイン回路のシミュレーションを参照。

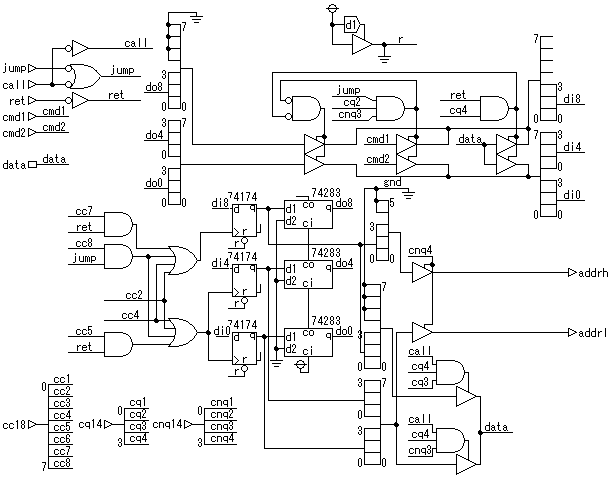

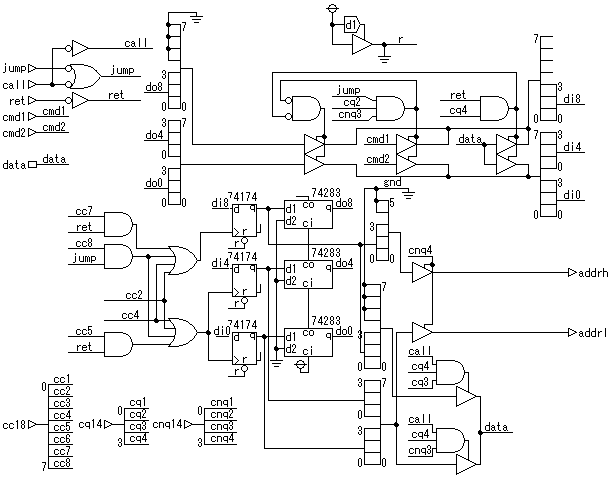

プログラムカウンタ(pc3)。

4ビットフリップフロップ(74174)を3つ用いている。インクリメントは3つの4ビット全加算器(74283)にキャリーから1を与える、同期型とした。フリップフロップの入力には3つの可能性、この全加算器からの信号・コマンド信号・データ信号がある。それぞれ、インクリメント・ジャンプ・リターンの各命令に相当する。この辺りの制御は、上のほうにある6つの3ステートにより行われている。出力側の制御としては、コマンド読み取りの際のアドレスライン出力と、コール命令の際にスタックに書き込むためのデータライン出力がある。ちなみに最上部、ディレイと3ステートでできた回路は、源内CAD限定のオートリセット回路。

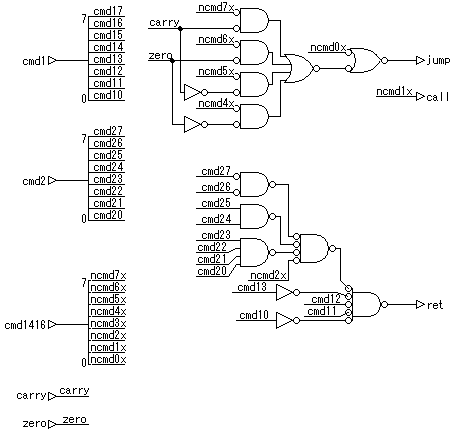

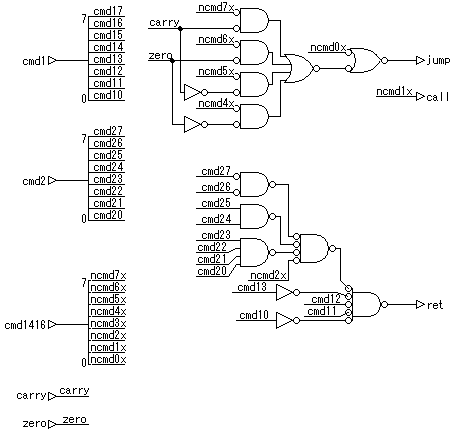

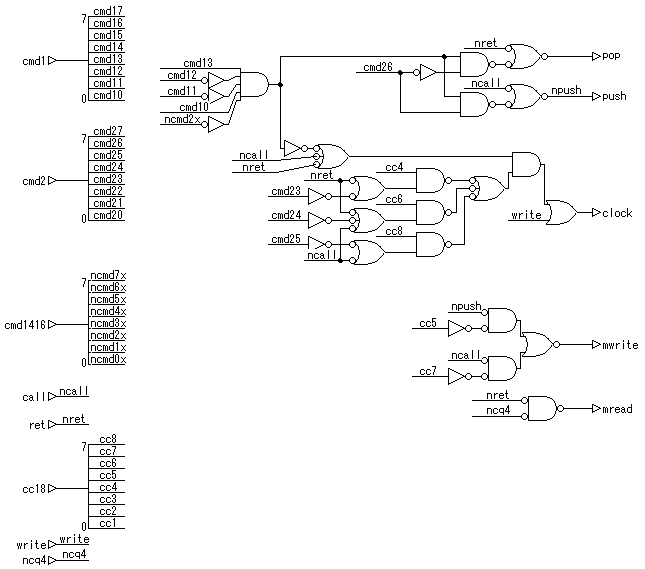

プログラムカウンタ・コントローラ(pccontrol)。

プログラムカウンタを有効にさせるための回路。後に、CPUの仕様が変更された場合に修正が楽になるよう、別のパーツとして作成した。特に難しい事はしていない。キャリー・ゼロのフラグを用いた条件分岐も、ここで行う。

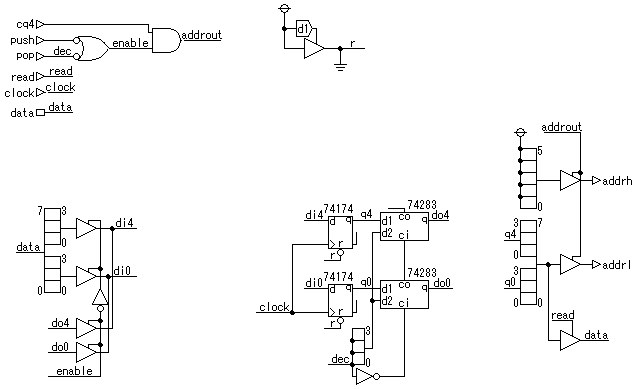

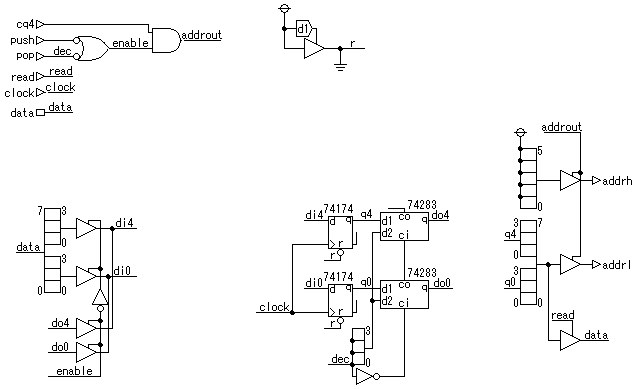

スタックポインタ(sp1)。

源内CADの使い方に慣れてきたのか、ずいぶんシンプルに書けた。4ビットのフリップフロップ2つと、4ビットの全加算器2つで構成されている。全加算器へのデータ及びキャリーは、インクリメントかデクリメントかで、異なる値を入力するようになっている。フリップフロップへの入力は、全加算器の出力かテータ入力かを選択するようにしてある。出力は、アドレスおよびデータの2つから選択。

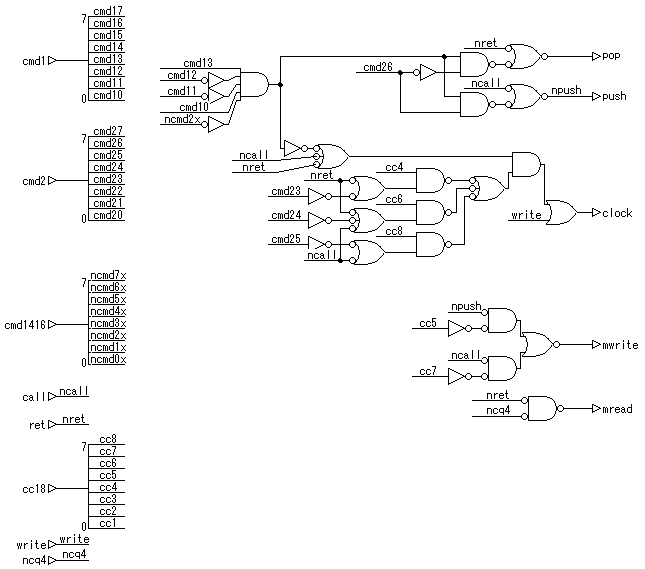

スタックポインタ・コントローラ(spcontroler)。

これも、特に難しい事はしていない。コマンドに従って、スタックポインタを制御するための回路。

これらの実装で、ジャンプ・コール・リターンが実行できた。いざやってみると、それぞれの実装部分は案外シンプルであり、まずまずの設計だといえそうだ。改めて回路を見て気がついたが、設計でリターン命令は0x3937となっているところ、この回路では0x393Fとしてしまっている。後で直さねばならない。

(<%media(20090919-main_0063_06.zip|ここからダウンロード)%>)

シミュレーションの結果は、次のとおり。

当然ながらひとつの図面では書ききれないので、いくつかのパーツに分解してある。74573と74138は、74シリーズの汎用ロジックICなので、説明は割愛。『i oc』『oc o』と書かれたパーツは、先に説明したオープンコレクタ部分の実装である。

左上から順に見てゆこう。まず、clock55。これはクロックジェネレータで、回路は次のとおり。

回路の上のほう、ディレイが8つ並んでいるのは、源内CAD限定の水晶発振回路。これを作成しシミュレートすると、『xxxxで発振しました』と警告が出て停止するが、reset信号のHの長さを適当に調整すると、警告は出なくなる。その後、このreset信号のHの長さを少しずつ長くしてゆけばよい。上記回路では、非同期でフリップフロップを繋げ、8つのシグナルに分周するようにした。8つのシグナルの入力部分で、2つのディレイを用いてトリガー信号を作成している。これは、メモリやレジスタへの書き込みなどのときに使うための信号であるが、このような実装にするのかどうかは実際の回路を組むときに再考する。動作結果は、先のメイン回路のシミュレーションを参照。

プログラムカウンタ(pc3)。

4ビットフリップフロップ(74174)を3つ用いている。インクリメントは3つの4ビット全加算器(74283)にキャリーから1を与える、同期型とした。フリップフロップの入力には3つの可能性、この全加算器からの信号・コマンド信号・データ信号がある。それぞれ、インクリメント・ジャンプ・リターンの各命令に相当する。この辺りの制御は、上のほうにある6つの3ステートにより行われている。出力側の制御としては、コマンド読み取りの際のアドレスライン出力と、コール命令の際にスタックに書き込むためのデータライン出力がある。ちなみに最上部、ディレイと3ステートでできた回路は、源内CAD限定のオートリセット回路。

プログラムカウンタ・コントローラ(pccontrol)。

プログラムカウンタを有効にさせるための回路。後に、CPUの仕様が変更された場合に修正が楽になるよう、別のパーツとして作成した。特に難しい事はしていない。キャリー・ゼロのフラグを用いた条件分岐も、ここで行う。

スタックポインタ(sp1)。

源内CADの使い方に慣れてきたのか、ずいぶんシンプルに書けた。4ビットのフリップフロップ2つと、4ビットの全加算器2つで構成されている。全加算器へのデータ及びキャリーは、インクリメントかデクリメントかで、異なる値を入力するようになっている。フリップフロップへの入力は、全加算器の出力かテータ入力かを選択するようにしてある。出力は、アドレスおよびデータの2つから選択。

スタックポインタ・コントローラ(spcontroler)。

これも、特に難しい事はしていない。コマンドに従って、スタックポインタを制御するための回路。

これらの実装で、ジャンプ・コール・リターンが実行できた。いざやってみると、それぞれの実装部分は案外シンプルであり、まずまずの設計だといえそうだ。改めて回路を見て気がついたが、設計でリターン命令は0x3937となっているところ、この回路では0x393Fとしてしまっている。後で直さねばならない。