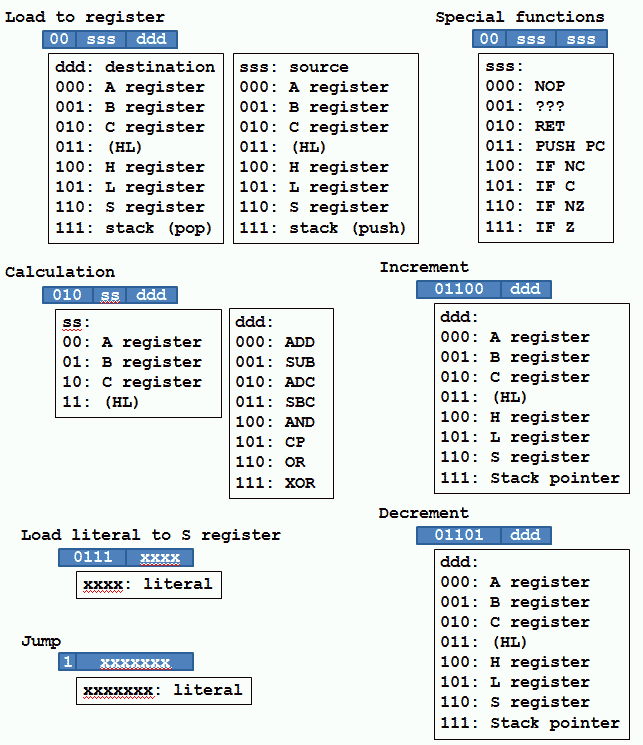

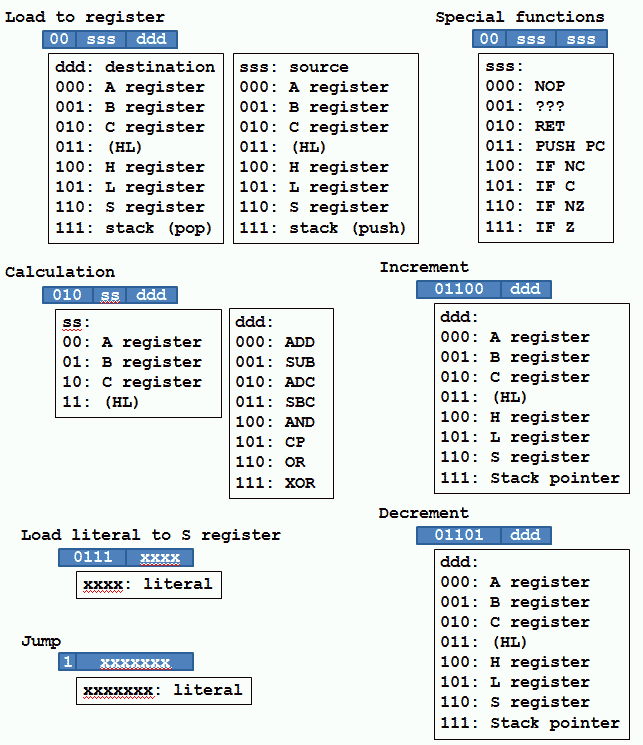

CPUの仕様を若干修正

2012年11月22日

CPLDで回路を組んでいる途中で気が付いたことに対応するため、命令の順を若干変更した。

変更したのは、演算命令のssの位置と、それに伴って上位3ビットを011から010に(こうすることで、ソースの指定が 0ss になる )したこと。ソースをbit3-5に固定、デスティネーションをbit0-2に固定するため、ロード命令のsssとdddを入れ替えたこと。インクリメント・デクリメントとリテラル値のSレジスタへの代入を余った領域に割り当て直したこと。

これらの変更で、回路が若干簡略化される。

変更したのは、演算命令のssの位置と、それに伴って上位3ビットを011から010に(こうすることで、ソースの指定が 0ss になる )したこと。ソースをbit3-5に固定、デスティネーションをbit0-2に固定するため、ロード命令のsssとdddを入れ替えたこと。インクリメント・デクリメントとリテラル値のSレジスタへの代入を余った領域に割り当て直したこと。

これらの変更で、回路が若干簡略化される。