クロック周り

2012年11月26日

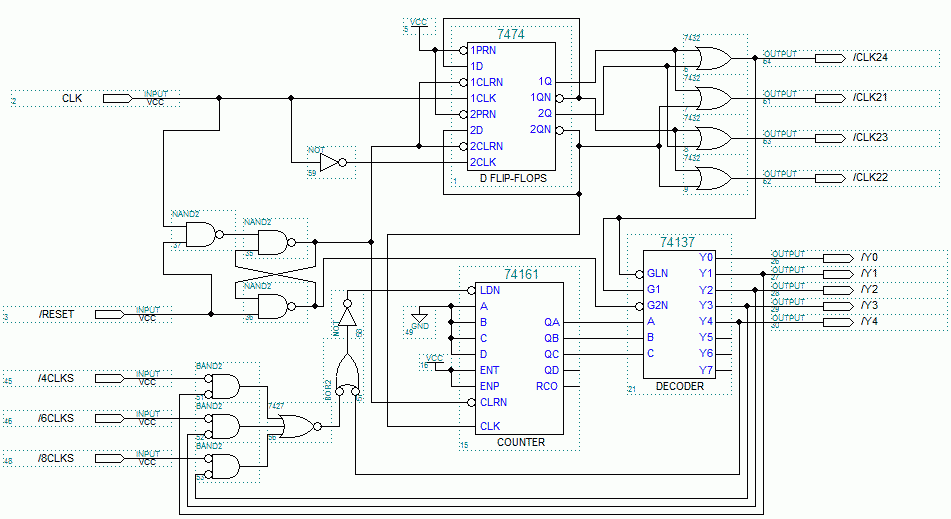

クロック作成部分は、とりあえず(というか、たぶん、ほぼ決まり)、こんな風に。

デコーダー(74137)のラッチ入力と出力許可(GLNとG1)が直結で入力されている部分が微妙なのだが、ラッチの入力から出力まである程度の遅延があるはずなので、たぶんこれでも大丈夫。後で必要なら、GLNの前に遅延回路を入れるかも知れない。

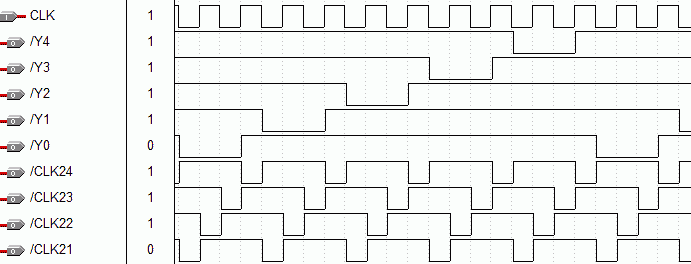

シミュレーションの結果は、次のようになる。

マシン語の命令の種類によって、4クロックから10クロック消費され、2クロックごとにY0, Y1, Y2, Y3, Y4が出力される。Y0-Y4それぞれがLになっている間バスに値が出力され、CLK22からのシグナルで、それぞれのラッチに値を入力する設計である。初期の設計では、Y0-Y4のシグナル幅が2クロックになっていたが、これを1.5クロックとすることで、瞬時ではあるものの、バスラインへの出力がかぶるようなことが無いようにした。

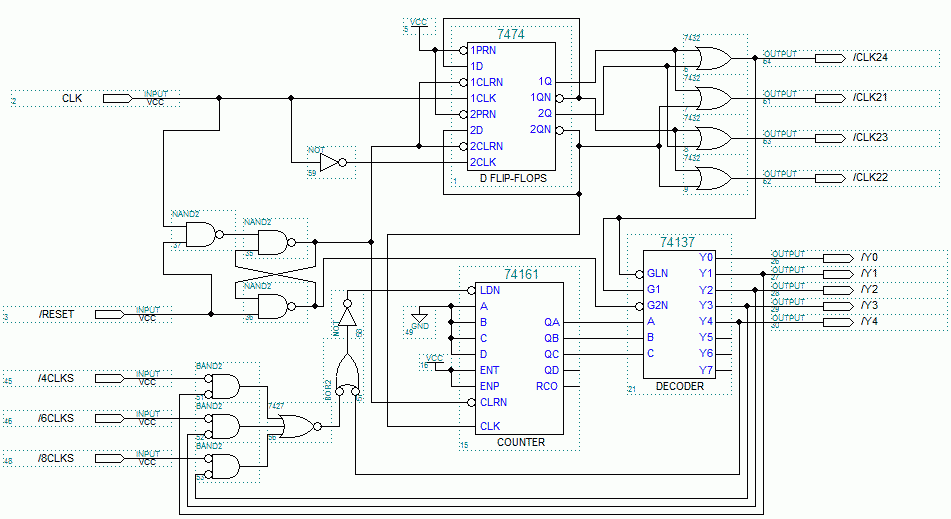

今のところ、タイミングはこんな風に。

デコーダー(74137)のラッチ入力と出力許可(GLNとG1)が直結で入力されている部分が微妙なのだが、ラッチの入力から出力まである程度の遅延があるはずなので、たぶんこれでも大丈夫。後で必要なら、GLNの前に遅延回路を入れるかも知れない。

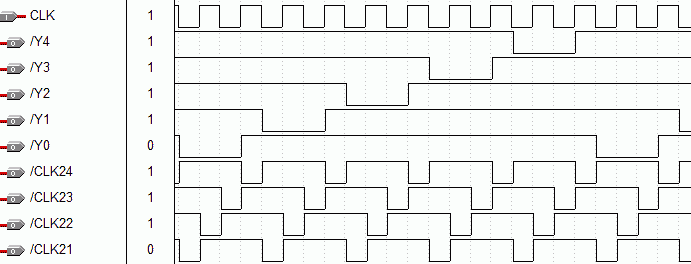

シミュレーションの結果は、次のようになる。

マシン語の命令の種類によって、4クロックから10クロック消費され、2クロックごとにY0, Y1, Y2, Y3, Y4が出力される。Y0-Y4それぞれがLになっている間バスに値が出力され、CLK22からのシグナルで、それぞれのラッチに値を入力する設計である。初期の設計では、Y0-Y4のシグナル幅が2クロックになっていたが、これを1.5クロックとすることで、瞬時ではあるものの、バスラインへの出力がかぶるようなことが無いようにした。

今のところ、タイミングはこんな風に。

Fetch code: Y0 CLK21: fetch code H Y0 CLK22: inc PC Y1 CLK21: fetch code L Y1 CLK22: inc PC NOP: Y2: reset IF C etc: Y1 CLK23: set skip flag Y2: reset Load literal: Y2 CLK22: load to S register Y3: reset PUSH: Y1 CLK23: dec SP Y2 CLK22: copy from register to memory Y3 reset POP: Y2 CLK22: load to register Y2 CLK23: inc SP Y3 reset Load to register: Y2 CLK22: copy to another register Y3: reset Calc: INC: DEC: Y2 CLK22: load to T register Y3 CLK22: copy T register to another register Y4: reset Jump: Y2 CLK22: load to PCS Y3 CLK22: load to PCH Y4 CLK22: load to PCL Y5: reset PUSH PC: Y1 CLK23: dec SP Y2 CLK22: copy from PCL to memory Y2 CLK23: dec SP Y3 CLK22: copy from PCH to memory Y3 CLK23: dec SP Y4 CLK23: copy from PCS to memory Y5: reset RET: Y2 CLK22: Load to PCS Y2 CLK23: inc SP Y3 CLK22: Load to PCH Y3 CLK23: inc SP Y4 CLK22: Load to PCL Y4 CLK23: inc SP Y5: reset