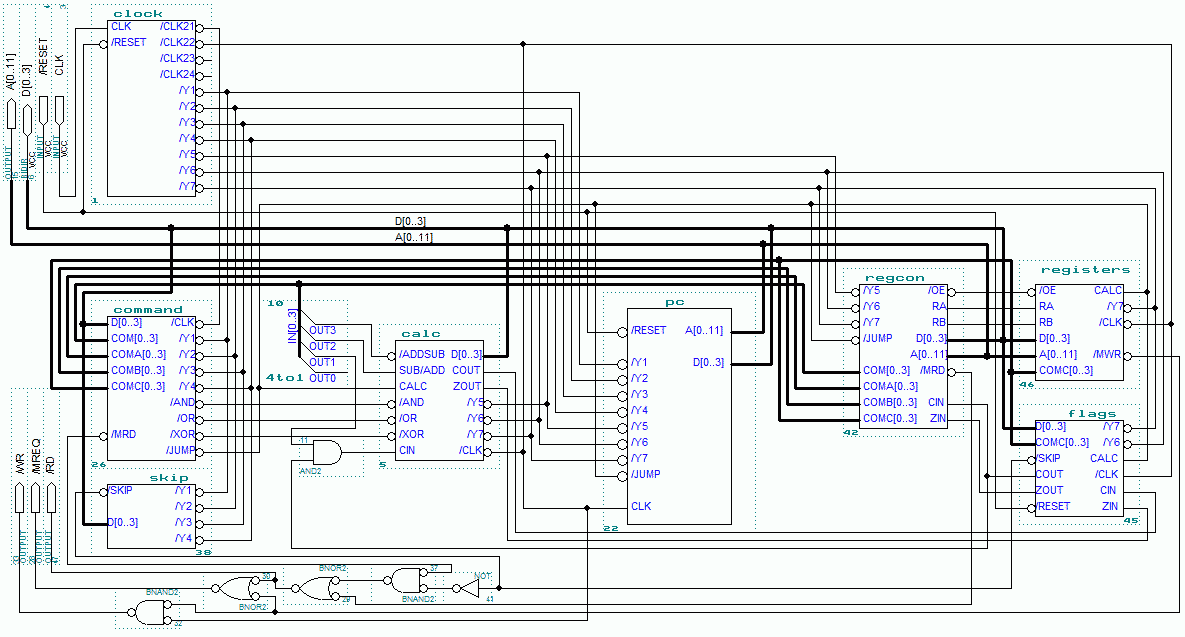

4 bit RISC CPUの回路

2012年12月11日

ほぼ、完成。 JUMP, CALC, SKIPなど、いくつかの命令が予想通り動くことを確認。

8つのブロックに分けてある。左上、clockは、水晶発振子からのシグナルを用い、7段階のステージ(Y1からY7)及び、4段階のサブステージ(CLK21-CLK24)のシグナルを送出する。左中央、commandは、命令を認識して、それぞれのブロックに細かな指令を出す。その下、skipは、フラグの値によって次の命令をスキップする場合に、NOP命令を作成する。

少し右、calcは、加減算とビット演算を行うための物。その右、pcは、プログラムカウンタ。

さらに右、regconは、commandからの指令に従って、レジスターブロック(regsters及びflags)に指令を出すための物。registersは12個のレジスター(x0,Y0,Z0,X1,Y1,Z1,X2,Y2,Z2,X3,Y3,Z3)を、flagsはキャリー・ゼロと、スキップフラグを格納している。

たぶんいらっしゃらないと思うが、各ブロックの中身がどうなっているか知りたい方は、ソースファイル(ver 0.2.0 ver 0.3.0)を参照されたい。Altera社の「Quartus II」か、「Max+PlusII」を用いて、見ることが出来る。

今後の予定としては、2通りの方向性がある。一つは、74シリーズの汎用ロジックを用いての構築への方向。現在の回路では、およそ65個のICが必要だが、回路を少し見直して、50個ぐらいに減らせないかと考えている。

もう一つの方向として、CPLDの使用マクロセル数を極力減らすと言うこと。今のままでは、512マクロセルのEPM3512にしかフィットしないので、これをEPM3256、あわよくばEPM3128に収まるようにしたい。また、最終的にMOS-FETで構築するときのことを考えて、なるだけ少ないトランジスタ数で構築出来るように、改変したい。

これら2つの方向性は、必ずしも同じ向きをむいているとは限らないので、並行して進めていくことになるかも知れない。

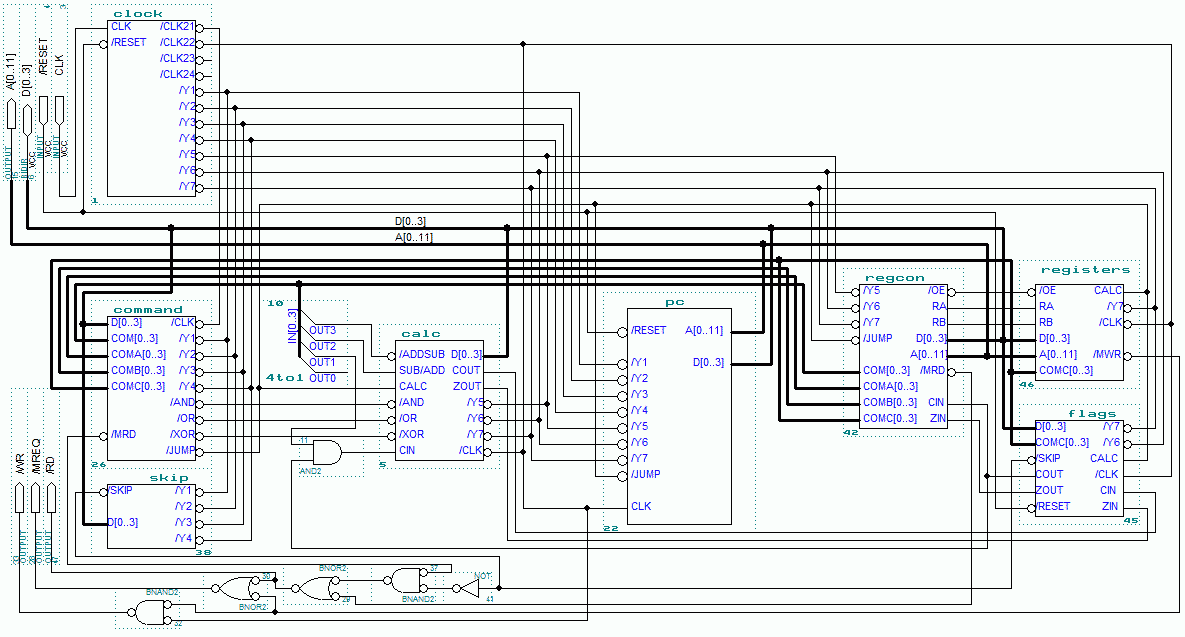

8つのブロックに分けてある。左上、clockは、水晶発振子からのシグナルを用い、7段階のステージ(Y1からY7)及び、4段階のサブステージ(CLK21-CLK24)のシグナルを送出する。左中央、commandは、命令を認識して、それぞれのブロックに細かな指令を出す。その下、skipは、フラグの値によって次の命令をスキップする場合に、NOP命令を作成する。

少し右、calcは、加減算とビット演算を行うための物。その右、pcは、プログラムカウンタ。

さらに右、regconは、commandからの指令に従って、レジスターブロック(regsters及びflags)に指令を出すための物。registersは12個のレジスター(x0,Y0,Z0,X1,Y1,Z1,X2,Y2,Z2,X3,Y3,Z3)を、flagsはキャリー・ゼロと、スキップフラグを格納している。

たぶんいらっしゃらないと思うが、各ブロックの中身がどうなっているか知りたい方は、ソースファイル(

今後の予定としては、2通りの方向性がある。一つは、74シリーズの汎用ロジックを用いての構築への方向。現在の回路では、およそ65個のICが必要だが、回路を少し見直して、50個ぐらいに減らせないかと考えている。

もう一つの方向として、CPLDの使用マクロセル数を極力減らすと言うこと。今のままでは、512マクロセルのEPM3512にしかフィットしないので、これをEPM3256、あわよくばEPM3128に収まるようにしたい。また、最終的にMOS-FETで構築するときのことを考えて、なるだけ少ないトランジスタ数で構築出来るように、改変したい。

これら2つの方向性は、必ずしも同じ向きをむいているとは限らないので、並行して進めていくことになるかも知れない。