IC・トランジスタで出来たコンピューターを設計・製作するためのブログ

| Jeans & Development | 電子ブロック工房 | 三日坊主 | フロントページ |

初めてのTQFP [一般的なこと]

2013年9月15日

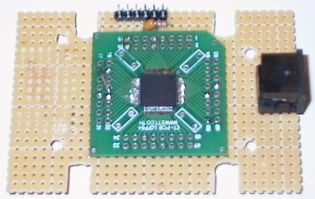

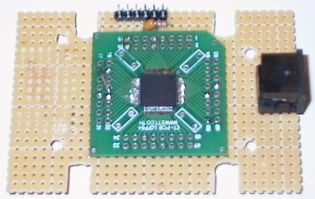

MicrochipのPIC32MX150F128Bは、DIPパッケージで、32 KBのRAMを搭載し32 bitのCPUが50 MHzで走る。DIPパッケージでこれだけの性能を持っているチップは例外中の例外で、私の知っている限りよそでは見あたらない。32 KB以上のRAMを持っている物は、QFNとかTQFPとか、表面実装のチップばかりである。

開発を続けているKM-Z80 miniは、現在の所28 KBのRAMを搭載したMZ-80Kをエミュレートしている。MZ-80Kは最大48 KBのRAMを搭載することが出来るので、KM-Z80 miniでも、ゆくゆくはこの容量のRAMを搭載したい。それには、52 KB以上のRAMを搭載したマイコンが必要であるが、残念ながらDIPパッケージでこれだけのRAMを持っている物は無いようだ。

大容量のRAMを実現する方法は、2つ。一つは、大容量RAMを持つチップを利用すること。もう一つは、RAMを外付けで利用すること。一つ目の方法を実現するには、DIPパッケージでは無理で、表面実装の物になる。二つ目の方法では、速度の速いパラレル接続を行うには、やはり表面実装のチップになる。これは、MIPSやARMなどの高速のCPUを持ち、かつI/Oピンの数の多いものは、やはり表面実装になるためである。他方で、ピン数の少ないSPI接続のRAMがPIC32MX150F128Bで使えるが(共に、DIPパッケージ)、この場合はデーターの読み込み速度が問題になる。2 MHzのZ80をエミュレートしているKM-Z80 miniでは何とかなりそうな気もしたが、いずれMZ-700のエミュレートも行うとすると、速度が追いつかない可能性が高い。

そういったことを考え、やはり表面実装のチップもちゃんと扱える用になっておいた方が良いだろうと考え、トライしてみた。

開発を続けているKM-Z80 miniは、現在の所28 KBのRAMを搭載したMZ-80Kをエミュレートしている。MZ-80Kは最大48 KBのRAMを搭載することが出来るので、KM-Z80 miniでも、ゆくゆくはこの容量のRAMを搭載したい。それには、52 KB以上のRAMを搭載したマイコンが必要であるが、残念ながらDIPパッケージでこれだけのRAMを持っている物は無いようだ。

大容量のRAMを実現する方法は、2つ。一つは、大容量RAMを持つチップを利用すること。もう一つは、RAMを外付けで利用すること。一つ目の方法を実現するには、DIPパッケージでは無理で、表面実装の物になる。二つ目の方法では、速度の速いパラレル接続を行うには、やはり表面実装のチップになる。これは、MIPSやARMなどの高速のCPUを持ち、かつI/Oピンの数の多いものは、やはり表面実装になるためである。他方で、ピン数の少ないSPI接続のRAMがPIC32MX150F128Bで使えるが(共に、DIPパッケージ)、この場合はデーターの読み込み速度が問題になる。2 MHzのZ80をエミュレートしているKM-Z80 miniでは何とかなりそうな気もしたが、いずれMZ-700のエミュレートも行うとすると、速度が追いつかない可能性が高い。

そういったことを考え、やはり表面実装のチップもちゃんと扱える用になっておいた方が良いだろうと考え、トライしてみた。

8 color 320x240 graphic display using PIC32MX [PIC]

2013年8月10日

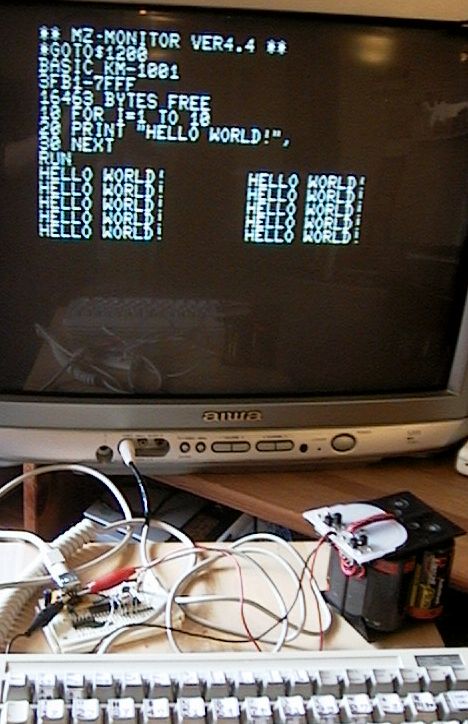

PIC32MX150F128Bを用いて、8色320x240ピクセルの、グラフィックディスプレイを作ってみた。

8色320x240ピクセルのデーター保存には最低288000バイト必要だから、PIC32MX150F128BのRAM容量・32768 bytesはぎりぎりである。同じPICマイコンを使ったグラフィックディスプレイとしては、ケンケンさんの32768色240x224ピクセルの作品があって、これは素晴らしい。今回の物は、性能的には劣るが、一石で仕上げるということ、目標とするMZ-700のディスプレイの規格は満たせること、私自身のカラービデオシグナル作成の勉強を兼ねるということで、8色320x240ピクセルで作ってみた。

8色320x240ピクセルのデーター保存には最低288000バイト必要だから、PIC32MX150F128BのRAM容量・32768 bytesはぎりぎりである。同じPICマイコンを使ったグラフィックディスプレイとしては、ケンケンさんの32768色240x224ピクセルの作品があって、これは素晴らしい。今回の物は、性能的には劣るが、一石で仕上げるということ、目標とするMZ-700のディスプレイの規格は満たせること、私自身のカラービデオシグナル作成の勉強を兼ねるということで、8色320x240ピクセルで作ってみた。

KM-Z80 mini version 0.3 [PIC]

2013年7月27日

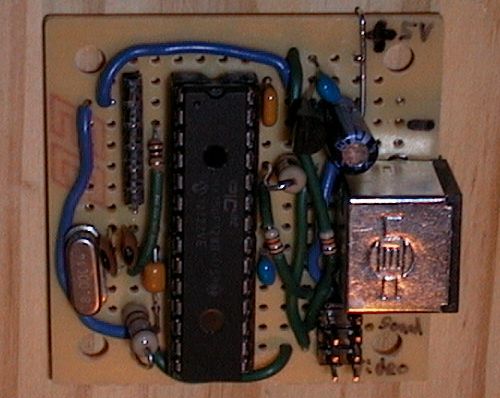

PIC32MXを用いたMZ-80K互換機の3号機が完成し、ほぼ安定して動くようになった。なお、回路図及びPICプログラムが若干変更になり、ver 0.3としている。

表側は、こんな感じ。左から、電源スイッチ、パイロットランプ(カナの時は赤)、PS/2キーボードコネクタ、テープレコーダー(もしくはiPod)入力端子。

表側は、こんな感じ。左から、電源スイッチ、パイロットランプ(カナの時は赤)、PS/2キーボードコネクタ、テープレコーダー(もしくはiPod)入力端子。

オマケ: ZK-MIPS mini (TK-80風、MIPS32 トレーニングキット) [PIC]

2013年7月27日

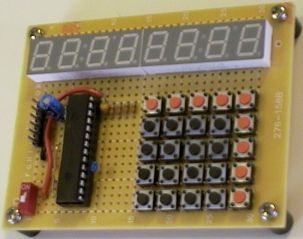

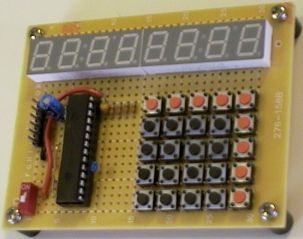

ZK-80 miniではMIPS32 CPUを内蔵したPIC32MXに、8080 CPUをエミュレーションさせている。MIPS32を内蔵した石であれば、MIPS32のプログラムを動かせるだろうということで、作ってみた。MIPSの命令を、ハンドアセンブルできる人限定のツール(笑)。

ZK-80 mini (PIC32MXを使った1チップTK-80互換機) [PIC]

2013年7月10日

ZK-80 miniを紹介します。NECのTK-80互換機で、Microchip社のPIC32MX120F032Bを用いて1チップで構成されています。

KM-Z80 mini version 0.2 [PIC]

2013年6月15日

KM-Z80 mini は、Microship の PIC32MX150F128B を用いた、1チップのSHARP MZ-80K 互換マイコンです。

最初の正式バージョンとして、version 0.2 を公開します。

KM-Z80 mini version 0.2 のダウンロードはこちらから。

ライセンスは、私がソースコードを書いた部分は、LGPL v2です。ただし、CG-ROMとモニターROMに関する部分は別のライセンスになっているので、注意して下さい。これらのROMデーターを取得したMZ-700 Emulatorのサイトによると、KM-Z80 mini は「営利を目的としない限り自由」に使用可能なライセンスで配布可能だと理解しています。

最初の正式バージョンとして、version 0.2 を公開します。

KM-Z80 mini version 0.2 のダウンロードはこちらから。

ライセンスは、私がソースコードを書いた部分は、LGPL v2です。ただし、CG-ROMとモニターROMに関する部分は別のライセンスになっているので、注意して下さい。これらのROMデーターを取得したMZ-700 Emulatorのサイトによると、KM-Z80 mini は「営利を目的としない限り自由」に使用可能なライセンスで配布可能だと理解しています。

KM-Z80 mini + カセットテープインターフェース [PIC]

2013年6月10日

KM-Z80 mini version 0.182 [PIC]

2013年2月10日

最新のPIC32MX150F128Bの仕様では、Max Speed MHz が 50 になっている。以前は40 MHzであったので、KM-Z80 miniも40 MHzで動かしていた。

この1.25倍の速度の違いが、KM-Z80 miniの開発に於いては非常に大きい。と言うのはPIC32MXの実行速度が、MZ-80Kをエミュレートするのにぎりぎりであったからである。CPUのリソースのうち、4割ほどがビデオシグナルの作成に取られていたため、残りの6割しかZ80-CPUのエミュレーションに使えなかった。この状態で、速度調整のためのウェイトルーチンをいっさい入れなかった場合に、かろうじておおよそ2 MHzでZ80が動いていた。

PIC32MXが、今までの1.25倍の速度で動くと、Z80のエミュレーションは1.25倍どころか、もっと速くなる。と言うのは、ビデオシグナル作成も速くなるため、より多くの時間をZ80のエミュレーションに費やすことができるようになるからだ。

この1.25倍の速度の違いが、KM-Z80 miniの開発に於いては非常に大きい。と言うのはPIC32MXの実行速度が、MZ-80Kをエミュレートするのにぎりぎりであったからである。CPUのリソースのうち、4割ほどがビデオシグナルの作成に取られていたため、残りの6割しかZ80-CPUのエミュレーションに使えなかった。この状態で、速度調整のためのウェイトルーチンをいっさい入れなかった場合に、かろうじておおよそ2 MHzでZ80が動いていた。

PIC32MXが、今までの1.25倍の速度で動くと、Z80のエミュレーションは1.25倍どころか、もっと速くなる。と言うのは、ビデオシグナル作成も速くなるため、より多くの時間をZ80のエミュレーションに費やすことができるようになるからだ。

KM-Z80 mini α version [PIC]

2012年12月23日

KM-Z80 mini + keyboard [PIC]

2012年12月16日